### **Introduction to FPGA**

### What is an FPGA?

- What FPGA can do:

- Can you use your Intel processor as an AMD processor tomorrow and again as an Intel processor the day after tomorrow?

- You receive software updates frequently, did you ever received a hardware update? Can you upgrade your core i5 to core i7?

- O Can you fix a bug in your chip after you have already received it?

#### What is an FPGA?

- FPGA is a "Programmable Hardware"

- As you do software programming to get the desired functionality, FPGA must be programmed to get the desired functionality.

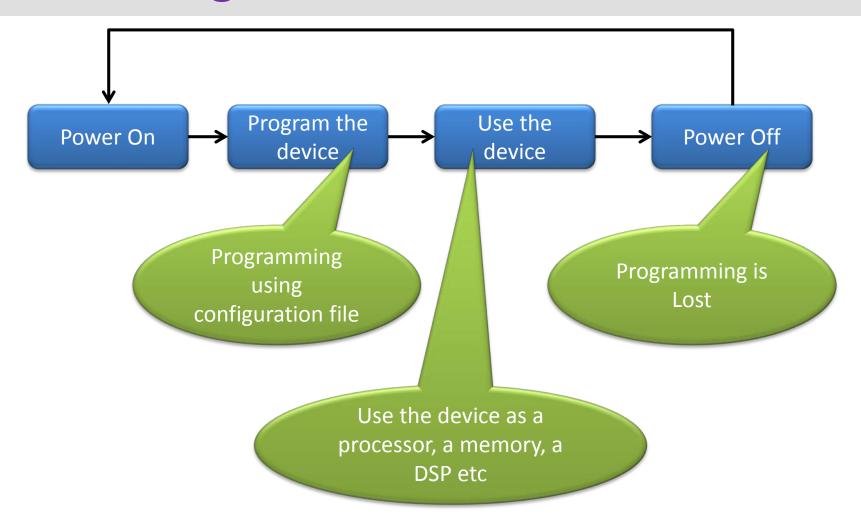

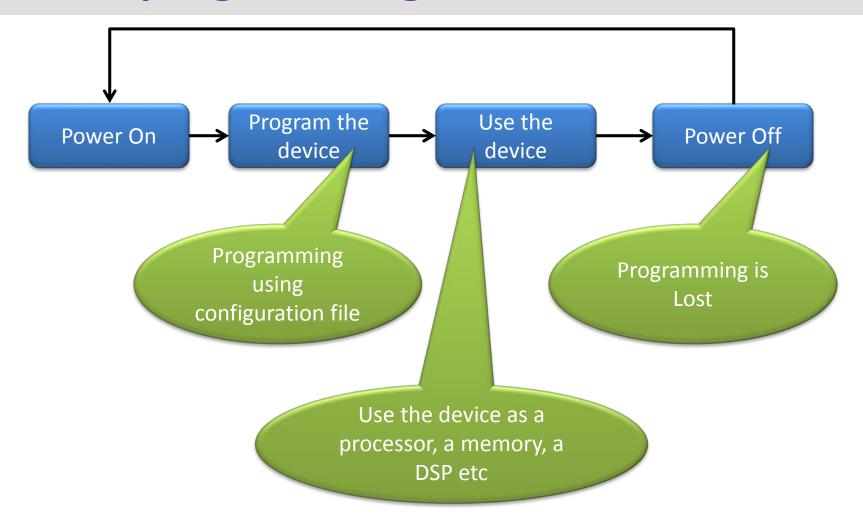

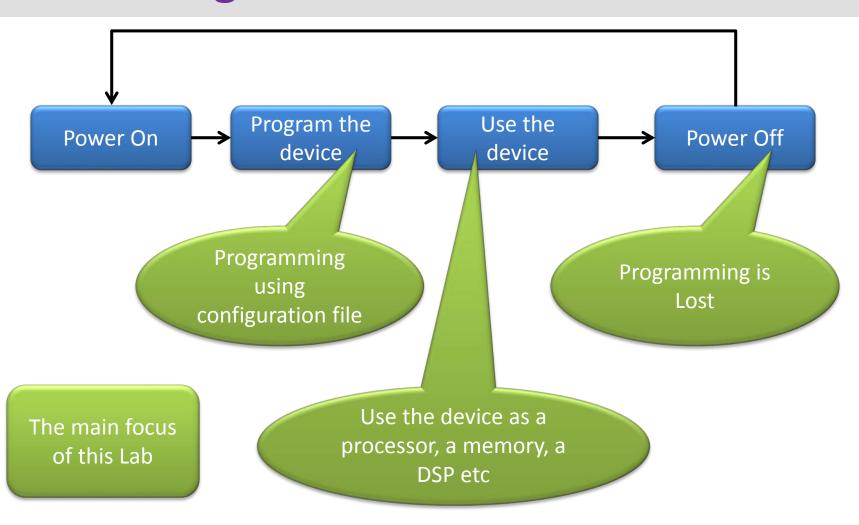

- At power-on FPGA is blank and cannot perform any task. It must be programmed to use as a particular hardware.

- Due to the "programmable" feature, the FPGA is highly flexible and upgradable.

## **Two main Companies**

### **FPGA** usage flow

### **FPGA** programming flow

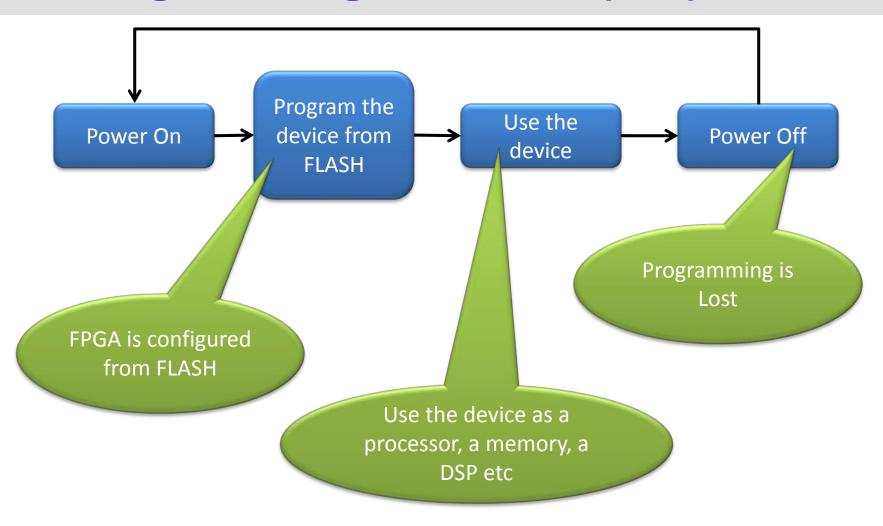

# Configure using FLASH file (.JIC)

### Altera FPGA programming flow

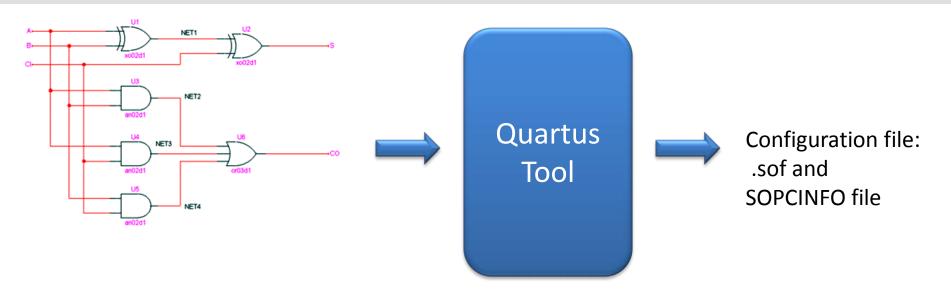

The Quartus tool takes your design as an input and generates configuration files ".sof" (SRAM Object File) and SOPCINFO (more on it later) files

### **FPGA** usage flow

### **FPGA** usage flow

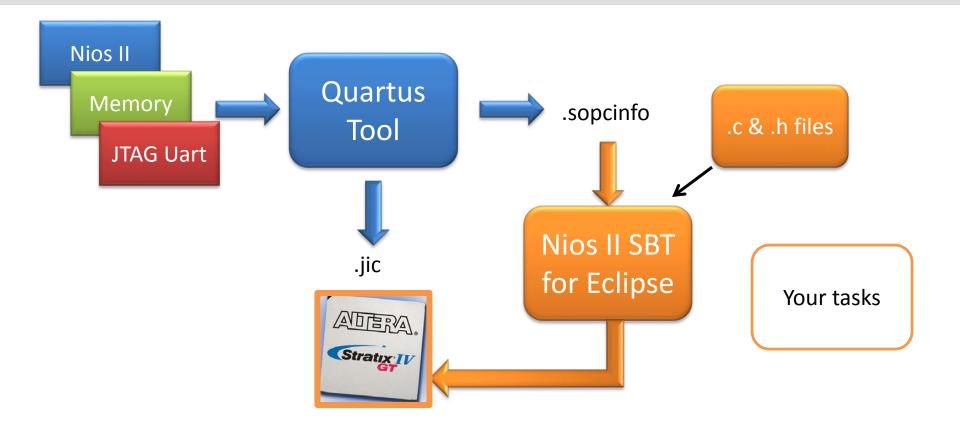

- In this lab course, we will provide SOPCINFO file and JIC file (flash programming file)

- Your tasks will be,

- Use the JIC file to configure (program) the FPGA

- Write a C code to program the processor (NIOS processor) on the FPGA

- Show us results

10

### Flow used in this lab course

## **Advantages of FPGA**

- Flexibility

- Upgradability

- Low cost for small projects

- Time to the market

- Prototyping

- High performance DSP algorithms

## **Disadvantages of FPGA**

- High cost for big projects

- Wastage of on-chip resources in programmable routing

- High power consumption compared to the same implementation on full custom design

- Low operating speed compared to the same implementation on full custom design

# Questions

#### **Control Panel**

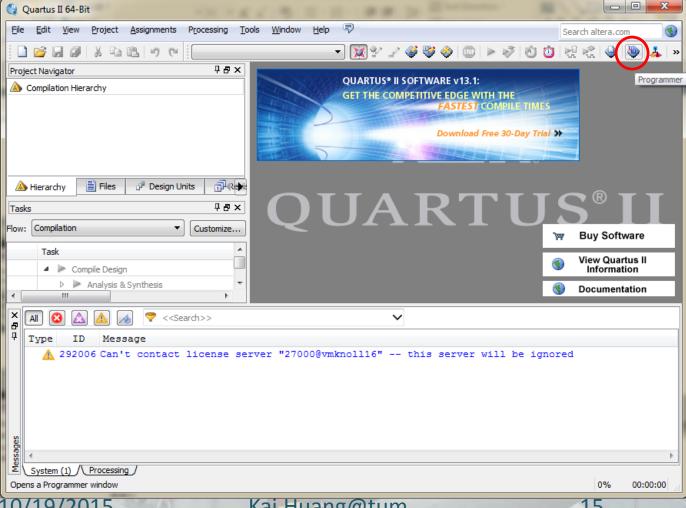

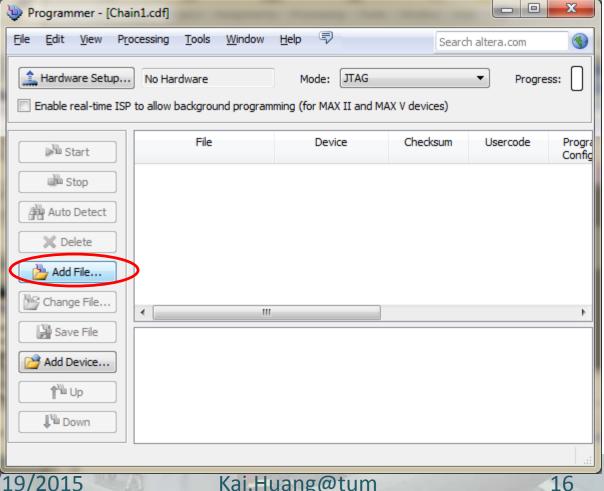

Program the FPGA using .SOF file:

#### **Control Panel**

Program the FPGA using .SOF file:

### Task overview: Your tasks

- Configure the FPGA using the provided JIC file

- Create a BSP project using SOPCINFO file

- Execute the "Hello world" C program on the NIOS core (feel free to use template)

# Questions