#### Industrial Embedded Systems - Design for Harsh Environment -

### Dr. Alexander Walsch alexander.walsch@ge.com IN 2244 Part VII WS 2015/16 Technische Universität München

#### **Software Architecture Design – IEC61508-3 Table A.2**

|     | Technique/Measure *                                                                                                      | Ref.         | SIL 1 | SIL 2 | SIL 3 | SIL 4 |

|-----|--------------------------------------------------------------------------------------------------------------------------|--------------|-------|-------|-------|-------|

|     | Architecture and design feature                                                                                          |              |       |       |       |       |

| 1   | Fault detection                                                                                                          | C.3.1        |       | R     | HR    | HR    |

| 2   | Error detecting codes                                                                                                    | C.3.2        | R     | R     | R     | HR    |

| 3a  | Failure assertion programming                                                                                            | C.3.3        | R     | R     | R     | HR    |

| 3b  | Diverse monitor techniques (with independence between<br>the monitor and the monitored function in the same<br>computer) | C.3.4        |       | R     | R     |       |

| 3c  | Diverse monitor techniques (with separation between the<br>monitor computer and the monitored computer)                  | C.3.4        |       | R     | R     | HR    |

| 3d  | Diverse redundancy, implementing the same software<br>safety requirements specification                                  | C.3.5        |       |       |       | R     |

| 3e  | Functionally diverse redundancy, implementing different<br>software safety requirements specification                    | C.3.5        |       |       | R     | HR    |

| 3f  | Backward recovery                                                                                                        | C.3.6        | R     | R     |       | NR    |

| 3g  | Stateless software design (or limited state design)                                                                      | C.2.12       |       |       | R     | HR    |

| 4a  | Re-try fault recovery mechanisms                                                                                         | C.3.7        | R     | R     |       |       |

| 4b  | Graceful degradation                                                                                                     | C.3.8        | R     | R     | HR    | HR    |

| 5   | Artificial intelligence - fault correction                                                                               | C.3.9        |       | NR    | NR    | NR    |

| 6   | Dynamic reconfiguration                                                                                                  | C.3.10       |       | NR    | NR    | NR    |

| 7   | Modular approach                                                                                                         | Table B.9    | HR    | HR    | HR    | HR    |

| 8   | Use of trusted/verified software elements (if available)                                                                 | C.2.10       | R     | HR    | HR    | HR    |

| 9   | Forward traceability between the software safety<br>requirements specification and software architecture                 | C.2.11       | R     | R     | HR    | HR    |

| 10  | Backward traceability between the software safety<br>requirements specification and software architecture                | C.2.11       | R     | R     | HR    | HR    |

| 11a | Structured diagrammatic methods **                                                                                       | C.2.1        | HR    | HR    | HR    | HR    |

| 11b | Semi-formal methods **                                                                                                   | Table B.7    | R     | R     | HR    | HR    |

| 11c | Formal design and refinement methods **                                                                                  | B.2.2, C.2.4 |       | R     | R     | HR    |

| 11d | Automatic software generation                                                                                            | C.4.6        | R     | R     | R     | R     |

| 12  | Computer-aided specification and design tools                                                                            | B.2.4        | R     | R     | HR    | HR    |

| 13a | Cyclic behaviour, with guaranteed maximum cycle time                                                                     | C.3.11       | R     | HR    | HR    | HR    |

| 13b | Time-triggered architecture                                                                                              | C.3.11       | R     | HR    | HR    | HR    |

| 13c | Event-driven, with guaranteed maximum response time                                                                      | C.3.11       | R     | HR    | HR    | -     |

| 14  | Static resource allocation                                                                                               | C.2.6.3      | -     | R     | HR    | HR    |

| 15  | Static synchronisation of access to shared resources                                                                     | C.2.6.3      | -     | -     | R     | HR    |

Source: IEC61508-3

A. Walsch IN2244 WS2015/16

### Fault Models

- A fault model determines what possible effects of faults on the behaviour of a system model are considered

- Hardware fault models are established

- Software fault models mainly deal with corruption of data flow or control flow

- Special attention is on communication (inter-task or via networks)

### Fault Detection

- Fault detection is a series of activities that happen at startup, background (cyclic tests) and specific maintenance cycles

- · CPU

- · Memory (used one)

- · 10

- Program sequence

- Basic method for fault detection evaluation is FMEA/FMEDA (hardware integrity and functionality)

- Time-critical test is cyclic background test since it checks physical resource during operation (must align to the process safety time specified in the systems requirements).

### **Diagnostic Coverage**

- · Specific to safety-related systems in industrial domain

- What is a DC (diagnostic coverage)?

- Hardware failures can lead to hazardous system states (not good!) which can result in harm (very bad!) – but they do not have to necessarily

- DC is the percentage of faults that are detected by checks;  $\lambda_{dd} = \lambda_d \times DC/100$

- If we can avoid a dangerous system failure by detecting dangerous component faults ( $\lambda_d$ ) in advance we can transfer  $\lambda_d$  into  $\lambda_s$  (if the application system allows for that).

- DC comes in four categories: no (<60%), low (60% < DC < 90%), medium (90% < DC < 99%), high (DC > 99%)

- Higher DC (IEC61508-2) -> influences PFD/PFH and architectural constraints

#### Hardware Failures – IEC615082 Table A.1

| Component                                          |                  | Requirements for diagnostic coverage claimed |                                                                                                                                         |                                                                                             |  |  |  |  |

|----------------------------------------------------|------------------|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|--|--|--|--|

| Component                                          | See<br>table(s)  | Low (60 %)                                   | Medium (90 %)                                                                                                                           | High (99 %)                                                                                 |  |  |  |  |

| Discrete hardware                                  | A.3, A.7,<br>A.9 |                                              |                                                                                                                                         |                                                                                             |  |  |  |  |

| Digital I/O                                        |                  | Stuck-at (see Note 1)                        | DC fault model (see<br>Note 2)                                                                                                          | DC fault model<br>drift and oscillation                                                     |  |  |  |  |

| Analogue I/O                                       |                  | Stuck-at                                     | DC fault model<br>drift and oscillation                                                                                                 | DC fault model<br>drift and oscillation                                                     |  |  |  |  |

| Power supply                                       |                  | Stuck-at                                     | DC fault model<br>drift and oscillation                                                                                                 | DC fault model<br>drift and oscillation                                                     |  |  |  |  |

| Bus                                                | A.3              |                                              |                                                                                                                                         |                                                                                             |  |  |  |  |

| General                                            | A.7              | Stuck-at of the<br>addresses                 | Time out                                                                                                                                | Time out                                                                                    |  |  |  |  |

| Memory<br>management unit<br>(MMU)                 | A.8              | Stuck-at of data or<br>addresses             | Wrong address<br>decoding<br>Change of addresses<br>caused by soft-errors in<br>the MMU registers (see<br>Notes 3 and 4)                | Wrong address decoding<br>Change of addresses caused by<br>soft-errors in the MMU registers |  |  |  |  |

| Direct memory<br>access (DMA)                      |                  | No or continuous<br>access                   | DC fault model for data<br>and addresses<br>Change of information<br>caused by soft-errors in<br>the DMA registers<br>Wrong access time | All faults that affect data in the<br>memory<br>Wrong access time                           |  |  |  |  |

| Bus-arbitration<br>(see Note 5)                    |                  | Stuck-at of arbitration<br>signals           | No or continuous<br>arbitration                                                                                                         | No or continuous or wrong<br>arbitration                                                    |  |  |  |  |

| Central Processing<br>Unit (CPU)                   | A.4, A.10        |                                              |                                                                                                                                         |                                                                                             |  |  |  |  |

| Register, internal<br>RAM                          |                  | Stuck-at for data and<br>addresses           | DC fault model for data<br>and addresses                                                                                                | DC fault model for data and<br>addresses                                                    |  |  |  |  |

|                                                    |                  |                                              | Change of information<br>caused by soft-errors                                                                                          | Dynamic cross-over for memory<br>cells                                                      |  |  |  |  |

|                                                    |                  |                                              |                                                                                                                                         | Change of information caused<br>by soft-errors                                              |  |  |  |  |

|                                                    |                  |                                              |                                                                                                                                         | No, wrong or multiple<br>addressing                                                         |  |  |  |  |

| Coding and<br>execution including<br>flag register |                  | Wrong coding or no<br>execution              | Wrong coding or wrong<br>execution                                                                                                      | No definite failure assumption                                                              |  |  |  |  |

| Address calculation                                |                  | Stuck-at                                     | DC fault model                                                                                                                          | No definite failure assumption                                                              |  |  |  |  |

|                                                    |                  |                                              | Change of addresses<br>caused by soft-errors                                                                                            |                                                                                             |  |  |  |  |

| Program counter,                                   |                  | Stuck-at                                     | DC fault model                                                                                                                          | DC fault model                                                                              |  |  |  |  |

| stack pointer                                      |                  |                                              | Change of addresses<br>caused by soft-errors                                                                                            | Change of addresses caused by<br>soft-errors                                                |  |  |  |  |

| Component                         | See      | Requirements for diagnostic coverage claimed |                                                              |                                                           |  |  |  |

|-----------------------------------|----------|----------------------------------------------|--------------------------------------------------------------|-----------------------------------------------------------|--|--|--|

| component                         | table(s) | Low (60 %) Medium (90 %)                     |                                                              | High (99 %)                                               |  |  |  |

| Interrupt handling                | A.4      |                                              |                                                              |                                                           |  |  |  |

| Interrupt                         |          | No or continuous<br>interrupts (see Note 6)  | No or continuous<br>interrupts                               | No or continuous interrupts<br>Cross-over of interrupts   |  |  |  |

|                                   |          |                                              | Cross-over of interrupts                                     | -                                                         |  |  |  |

| Reset circuitry                   |          | Stuck-at                                     | DC fault model                                               | DC fault model                                            |  |  |  |

|                                   |          | Individual components                        | Drift and oscillation                                        | Drift and oscillation                                     |  |  |  |

|                                   |          | do not initialize to reset<br>state          | Individual components<br>do not initialize to reset<br>state | Individual components do not<br>initialize to reset state |  |  |  |

| Invariable memory                 | A.5      | Stuck-at for data and<br>addresses           | DC fault model for data<br>and addresses                     | All faults that affect data<br>in the memory              |  |  |  |

| Variable memory                   | A.6      | Stuck-at for data and<br>addresses           | DC fault model for data<br>and addresses                     | DC fault model for data and<br>addresses                  |  |  |  |

|                                   |          |                                              | Change of information<br>caused by soft-errors               | Dynamic cross-over for memory<br>cells                    |  |  |  |

|                                   |          |                                              |                                                              | Change of information caused<br>by soft-errors            |  |  |  |

|                                   |          |                                              |                                                              | No, wrong or multiple<br>addressing                       |  |  |  |

| Clock (quartz,                    | A.11     | Sub- or super-harmonic                       | Incorrect frequency                                          | Incorrect frequency                                       |  |  |  |

| oscillator, PLL)                  |          | Period jitter                                | Period jitter                                                | Period jitter                                             |  |  |  |

| Communication and<br>mass storage | A.12     | Wrong data or<br>addresses                   | All faults that affect data<br>in the memory                 | All faults that affect data<br>in the memory              |  |  |  |

|                                   |          | No transmission                              | Wrong data or                                                | Wrong data or addresses                                   |  |  |  |

|                                   |          |                                              | addresses                                                    | Wrong transmission time                                   |  |  |  |

|                                   |          |                                              | Wrong transmission<br>time                                   | Wrong transmission sequence                               |  |  |  |

|                                   |          |                                              | Wrong transmission<br>sequence                               |                                                           |  |  |  |

| Sensors                           | A.13     | Stuck-at                                     | DC fault model                                               | DC fault model                                            |  |  |  |

|                                   |          |                                              | Drift and oscillation                                        | Drift and oscillation                                     |  |  |  |

| Final elements                    | A.14     | Stuck-at                                     | DC fault model                                               | DC fault model                                            |  |  |  |

|                                   |          |                                              | Drift and oscillation                                        | Drift and oscillation                                     |  |  |  |

Source: IEC61508-2

#### A. Walsch IN2244 WS2015/16

### **CPUs – IEC6108-2 Table A.4, A.10**

| Diagnostic<br>technique/measure                                       | See<br>IEC 61508-7 | Maximum diagnostic coverage<br>considered achievable | Notes                                    |

|-----------------------------------------------------------------------|--------------------|------------------------------------------------------|------------------------------------------|

| Comparator                                                            | A.1.3              | High                                                 | Depends on the quality of the comparison |

| Majority voter                                                        | A.1.4              | High                                                 | Depends on the quality of the voting     |

| Self-test by software:<br>limited number of<br>patterns (one channel) | A.3.1              | Low                                                  |                                          |

| Self-test by software:<br>walking bit<br>(one-channel)                | A.3.2              | Medium                                               |                                          |

| Self-test supported by hardware (one-channel)                         | A.3.3              | Medium                                               |                                          |

| Coded processing<br>(one-channel)                                     | A.3.4              | High                                                 |                                          |

| Reciprocal comparison<br>by software                                  | A.3.5              | High                                                 | Depends on the quality of the comparison |

|                                                                             |       | Maximum diagnostic coverage<br>considered achievable | Notes                                       |

|-----------------------------------------------------------------------------|-------|------------------------------------------------------|---------------------------------------------|

| Watch-dog with separate<br>time base without time-<br>window                | A.9.1 | Low                                                  |                                             |

| Watch-dog with separate<br>time base and time-<br>window                    | A.9.2 | Medium                                               |                                             |

| Logical monitoring of<br>program sequence                                   | A.9.3 | Medium                                               | Depends on the quality of<br>the monitoring |

| Combination of temporal<br>and logical monitoring of<br>programme sequences | A.9.4 | High                                                 |                                             |

| Temporal monitoring with<br>on-line check                                   | A.9.5 | Medium                                               |                                             |

### Invariable Memory – IEC6108-2 Table A.5

| Diagnostic<br>technique/measure          | See<br>IEC 61508-7 | Maximum diagnostic coverage<br>considered achievable | Notes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                    |

|------------------------------------------|--------------------|------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| Word-protection multi-<br>bit redundancy | A.4.1              | Medium                                               | The effectiveness of the Word-<br>protection multi-bit redundancy<br>depends on the inclusion of the<br>word address into the multiple bit<br>redundancy, and relies on<br>respective measure to detect multi-<br>bit common cause faults, e.g.<br>multiple addressing (multiple row<br>select, multiple local to global bit<br>line switches activated), power<br>supply issues (e.g. charge pump<br>flaws), production row and column<br>replacement (production yield<br>measure to mask production faults),<br>etc. |                    |

| Modified checksum                        | A.4.2              | Low                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                    |

| Signature of one word<br>(8-bit)         | A.4.3              | Medium                                               | The effectiveness of the signature<br>depends on the width of the<br>signature in relation to the block<br>length of the information to be<br>protected                                                                                                                                                                                                                                                                                                                                                                 | Source: IEC61508-2 |

| Signature of a double<br>word (16-bit)   | A.4.4              | High                                                 | The effectiveness of the signature<br>depends on the width of the<br>signature in relation to the block<br>length of the information to be<br>protected                                                                                                                                                                                                                                                                                                                                                                 |                    |

| Block replication                        | A.4.5              | High                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                    |

#### Variable Memory – IEC6108-2 Table A.6

| Diagnostic<br>technique/measure                                                                                                        | See<br>IEC 61508-7 | Maximum diagnostic coverage<br>considered achievable | Notes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------------------------------------------------------------------------------------------------------------------------------------|--------------------|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RAM test checkerboard or<br>march                                                                                                      | A.5.1              | Low                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| RAM test walk-path                                                                                                                     | A.5.2              | Medium                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| RAM test galpat or<br>transparent galpat                                                                                               | A.5.3              | High                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| RAM test Abraham                                                                                                                       | A.5.4              | High                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Parity-bit for RAM                                                                                                                     | A.5.5              | Low                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| RAM monitoring with a<br>modified Hamming code,<br>or detection of data<br>failures with error-<br>detection-correction<br>codes (EDC) | A.5.6              | Medium                                               | The effectiveness of the RAM<br>monitoring with a modified<br>Hamming code, or detection of<br>data failures with error detection-<br>correction codes (EDC) depends<br>on the inclusion of the address<br>into the Hamming code, and relies<br>on respective measure to detect<br>multi-bit common cause faults, e.g.<br>multiple addressing (multiple row<br>select, multiple local to global bit<br>line switches activated),<br>production row and column<br>replacement (production yield<br>measure to mask production<br>faults), etc. |

| Double RAM with<br>hardware or software<br>comparison and<br>read/write test                                                           | A.5.7              | High                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

Source: IEC61508-2

### Memory

- Parameter memory (non volatile)

- EEPROM byte wise read and write holds e.g. configuration parameters, run-time parameters (hour meter, status)

- Program memory (non volatile)

- Flash (NOR)– word wise read, write requires a block erase holds executable (XIP – execute in place)

- Data memory (volatile)

- RAM (SRAM) word wise read and write addressable holds data and stack

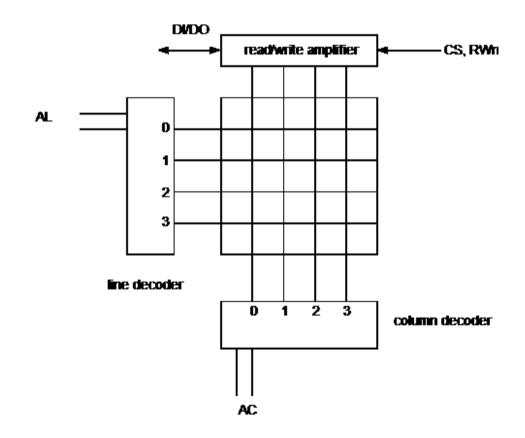

### Fault Detection - Memory Model-

- Memory matrix organization

- (1-bit ... n-bit) in reality one data word stored at a specific address

- address decoder, read and write amplifiers, control signals, data in and out

- low diagnostic coverage: stuck-at for data and/or address (constantly '0' or '1')

- medium diagnostic coverage: DC fault model for data and address (stuck-at, high-Z, X-talk)

## Fault Detection - Non-variable Memory (program memory) -

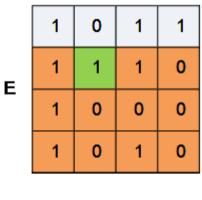

- Modified checksum test, based on XOR and circular shift operations

- Defined checksum is compared to the checksum calculated during operation

- Odd-numbered bit errors within a column are detected

- Low diagnostic coverage test

A. Walsch IN2244 WS2015/16

# Fault Detection - Non-variable Memory (program memory) II -

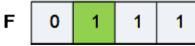

- Signature of one word test (CRC), based on Modulo-2 arithmetic

- Memory content is interpreted as a bit stream

- Division by a defined polynomial yields zero, P(X) = 11001 in this example

- All one bit and multi-bit failures within one word and 99.6% of all possible bit failures are detected

- Medium diagnostic coverage test

A. Walsch IN2244 WS2015/16

### Fault Detection - Non-variable memory (EEPROM) -

- EEPROM content is copied to SRAM and verified during system initialization -> working copy

- All changes are made to working copy

- Working copy is written to EEPROM before power-down or at defined slow cycles (wear-out effect!)

- EEPROM test is reduced to a RAM test we work from RAM data

### Fault Detection - Variable memory (SRAM) -

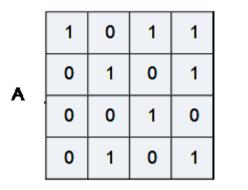

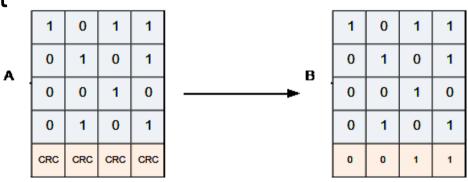

- Checkerboard test low diagnostic coverage

- Cells are checked for correct content in pairs

- Initialization, upward test, downward test, inverse initialization, upward test, downward test -> 10 \* n complexity (number of load store operations)

- Pairs are address inverse

### Fault Detection - Variable memory (SRAM) II -

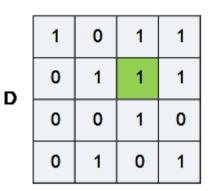

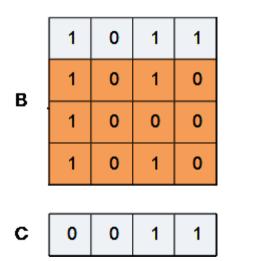

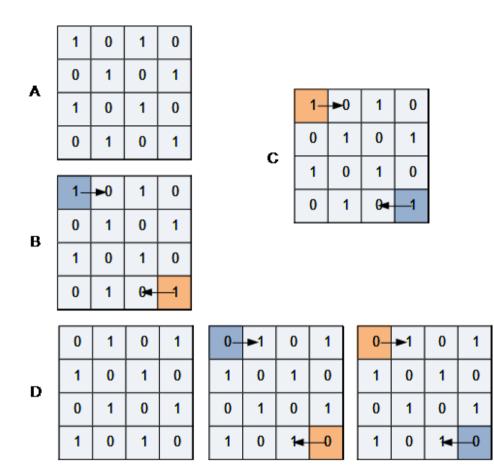

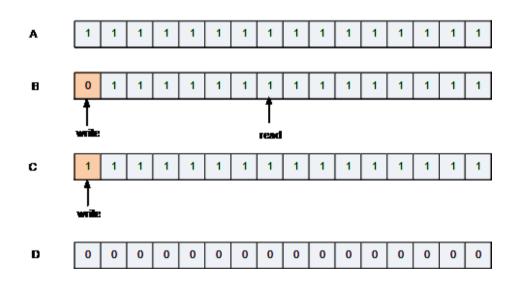

- Walking pattern medium diagnostic coverage

- Initialization (A), the first cell is inverted and all cells are checked for correct content (B), the first cell is inverted again (C), the test is conducted again with inverse background (D) -> 2\*n\*n + 6\*n complexity (number of load store operations)

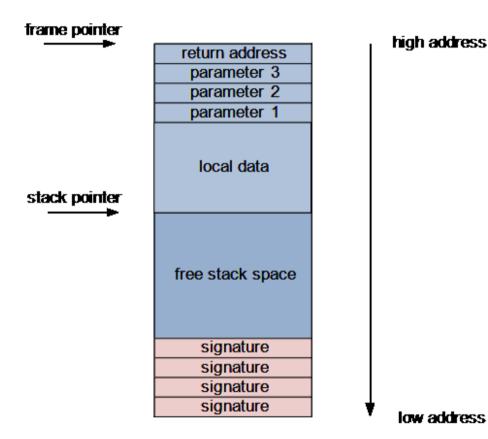

### Fault Detection - Variable memory (Stack) -

Stack data integrity is checked by correct program flow (the stack stores our task context)

Stack limits are checked by signature or addresses (some controllers provide hardware support)

Underlying hardware (SRAM) is checked by SRAM tests

#### Fault Detection - Example -

RAM tests are destructive – therefore we need to safe the original data in advance

| D:\embedded_group\PMU\source\ram_test.c                                               |    | • 🚞 Watch |         |               |        |   |   |

|---------------------------------------------------------------------------------------|----|-----------|---------|---------------|--------|---|---|

| /* public function bodies                                                             | */ | Add SFR A | CCA 🔽 A | dd Symbol mem |        |   | • |

| /*                                                                                    | */ | Update    | Address | Symbol Name   | Value  |   |   |

| intl6 Walking Pattern()                                                               |    |           | 0800    | 🗆 mem         |        |   |   |

|                                                                                       |    |           | 0800    |               | 0x5555 |   | - |

| intl6 i, k;                                                                           |    | •         | 0802    | [1]           | OxAAAA |   |   |

|                                                                                       |    | · .       | 0804    | [2]           | OxAAAA |   |   |

| /* first part: write l into all memory cells */                                       |    | ·         | 0806    | [3]           | OXAAAA |   |   |

| /* write 0 into exactly one */                                                        |    | 1         | 0808    | [4]           | OXAAAA |   |   |

| /* read all cells and look verify correctness */                                      | _  |           | 080A    |               | OXAAAA |   |   |

| for (i=0; i< RAM_SIZE ; i++) {                                                        |    |           | 080C    | [6]           | OXAAAA |   |   |

| $*(\mathbf{mem}+\mathbf{i}) = 0 \times \mathbf{A} \mathbf{A} \mathbf{A} \mathbf{A}; $ |    |           | 080E    | [7]           | OXAAAA |   |   |

| <b>B</b> for (i=0; i< RAM SIZE ; i++) (                                               |    |           | 0810    | [8]           | OXAAAA |   |   |

| <b>for</b> $(1=0)$ 1< RAM_S12R ; 1++) {<br>*(mem+i) = 0x5555;                         |    | 1         | 0812    | [9]           | OXAAAA |   |   |

| for (k=0; k< RAM SIZE ; k++) {/*read*/                                                |    |           | 0814    | [10]          | OXAAAA |   |   |

| <b>if</b> ( <b>k</b> == <b>i</b> ) {                                                  |    |           | 0816    | [11]          | OXAAAB |   |   |

| continue; /*skip*/                                                                    |    |           | 0818    | [12]          | OXAAAA |   |   |

| }                                                                                     |    |           | 081A    | [13]          | OXAAAA |   |   |

| <b>else</b> (/*k/=i*/                                                                 |    |           | 081C    | [14]          | OXAAAA |   |   |

| if(*(mem+k) == 0xAAAA)(                                                               |    |           | 081E    | [15]          | OXAAAA |   |   |

| continue; /*good*/                                                                    |    |           | 0820    | [16]          | OXAAAA |   |   |

| }                                                                                     |    |           | 0822    | [17]          | OXAAAA |   |   |

| else(                                                                                 |    |           | 0824    | [18]          | OXAAAA |   |   |

| return (-1); /*bad*/                                                                  |    |           | 0826    | [19]          | OXAAAA |   |   |

| }                                                                                     |    |           | 0828    | [20]          | OXAAAA |   |   |

| , ,                                                                                   |    |           | 082A    | [21]          | OXAAAA |   |   |

| <pre>/*(mem+i) = OxAAAA; /*reset memory*/</pre>                                       |    |           | 082C    | [22]          | OXAAAA |   |   |

| (memory) = OXXXXX, / "reset memory"/                                                  |    | 1         | 082E    | [23]          | OXAAAA |   |   |

| /* second part: write 0 into all memory cells */                                      |    | 1         | 0830    | [24]          | OxAAAA |   |   |

| /* write 1 into exactly one */                                                        |    |           | 0832    | [25]          | OxAAAA |   |   |

| /* read all cells and look verify correctness */                                      |    |           | 0834    | [26]          | OxAAAA |   |   |

| <pre>for (i=0; i &lt; RAM_SIZE ; i++) {</pre>                                         |    |           | 0836    | [27]          | OxAAAA |   |   |

| *(mem+i) = 0x5555; }                                                                  | _  |           | 0838    | [28]          | OXAAAA |   |   |

|                                                                                       |    |           | 083A    | [29]          | OXAAAA |   |   |

|                                                                                       |    |           | 083C    | [30]          | OXAAAA |   |   |

| #define APP_PRIVATE_CONSTANT_1 1                                                      |    | 1         | 083E    | [31]          | OXAAAA |   |   |

| pols #define APP_PRIVATE_CONSTANT_2 2                                                 |    |           | 0840    | [32]          | OXAAAA |   |   |

| EXECUTING #define APP_PRIVATE_CONSTANT_3 3                                            |    |           | 0842    | [33]          | OXAAAA |   |   |

|                                                                                       |    |           | 0844    | [34]          | OXAAAA | 1 |   |

| /*                                                                                    |    | - III     | 0047    | 1051          | 0      |   | Ī |

bit flip

### Communication - Error Detection -

- We usually use standard protocols to transmit data.

Correctness is guaranteed by by error detection mechanisms (e.g. parity, CRC)

- Sometimes error detection capability not sufficient

- Hamming distance of n: n-1 bit errors can be detected.

- Residual error: If we do know the Hamming distance and do know the bit error rate (bit flips are statistically independent) we can calculate a residual error.

- CRC: an additional peace of data is added to the existing bit stream.

The additional peace of data allows error detection

|                      |              | Probability of bit failures p         | Transmission medium             |             |  |

|----------------------|--------------|---------------------------------------|---------------------------------|-------------|--|

| payload              | •            | $> 10^{-3}$                           | Transmission path               |             |  |

|                      |              | 10 <sup>-4</sup> Unscreened data line |                                 |             |  |

| Address              |              | $10^{-5}$<br>$10^{-6} - 10^{-7}$      | Screened twisted-pair telephon  |             |  |

| 8 bit Data – 128 bit | CRC – 16 bit |                                       | Digital telephone circuit (ISD) |             |  |

| 8 DIL                |              | 10-9                                  | Coaxial cable in local defined  | application |  |

| •                    |              | 10 <sup>-12</sup>                     | Fibre optic cable               |             |  |

| transmitted data     |              |                                       | Source:                         |             |  |

|                      |              | 244 WS2015/16                         |                                 | 19          |  |

|                      |              | 244 0032013/10                        | Börcsök, HIMA                   | 19          |  |

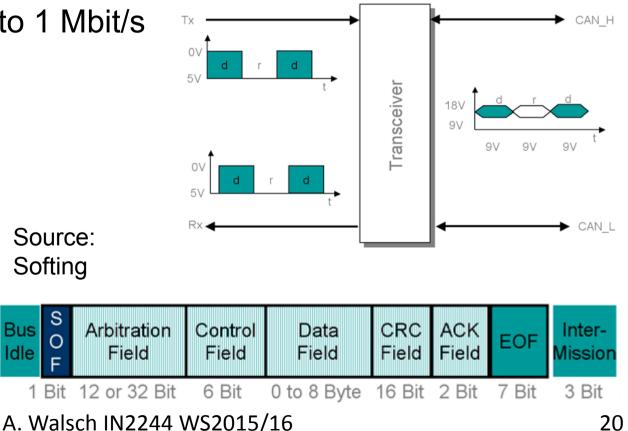

### Communication - CAN -

CAN: Controller Area Network, ISO 11898 (PHY, DLL)

S

Bus

Idle

- Protocol controller available as peripheral of embedded processors, line driver external (creates differential signals, adds protection circuits)

- Serial protocol, up to 1 Mbit/s

- **Bit-wise arbitration**

- Error detection

#### Source: Application - device 1 Application - device 2 Safety Standard Safety Standard MESCO Engineering, Forum Funktionale Safety Sicherheit 2013 Safety Safety communication layer protocol protocol Standard protocol Standard protocol Black channel Deterministic remedial measures Time expectation (Watchdog) Redundancy checking Sequence number Data integrity assurance (CRC) Different data integrity assurance systems Time stamp Connection authentication Feedback message (Echo) with Error I Cross Х х Х Unintended repetition Loss Х Х Х х х х х Insertion Х х Х Incorrect sequence х Corruption Unacceptable delay Х х х Х х Masquerade Adressing Х

### **Black Channel**

21

#### Proven in use Software (FAQs – www.iec.ch)

D11) Can an E/E/PE safety-related system contain hardware and/or software that was not produced according to IEC 61508, and still comply with the standard (proven in use)?

It may be possible to use a *proven in use* argument as an alternative to meeting the design requirements for dealing with systematic failure causes in IEC 61508, including hardware and software. But it is essential to note that proven in use cannot be used as an alternative to meeting the requirements for:

- architectural constraints on hardware safety integrity (see 7.4.2.1 of IEC 61508-2);

- the quantification of dangerous failures of the safety function due to random hardware faults (see 7.4.3.2 of IEC 61508-2); and

- system behaviour on detection of faults (see 7.4.6 of IEC 61508-2).

See 7.4.2.2 of IEC 61508-2 for a summary of design requirements, including references to more detailed systematic hardware requirements in the standard.

A proven in use claim relies on the availability of historical data for both random hardware and systematic failures, and on analytical techniques and testing if the previous conditions of use of the subsystem differ in any way from those which will be experienced in the E/E/PE safety-related system. 7.4.7.6 of IEC 61508-2 requires that:

- the previous conditions of use of the subsystem are the same as, or sufficiently close to, those which will be experienced in the E/E/PE safety-related system (see 7.4.7.7 of IEC 61508-2);

- if the above conditions of use differ in any way, a demonstration is necessary (using a combination of appropriate analytical techniques and testing) that the likelihood of unrevealed systematic faults is low enough to achieve the required safety integrity level of the safety functions which use the subsystem (see 7.4.7.8 of IEC 61508-2);

- the claimed failure rates have sufficient statistical basis (see 7.4.7.9 of IEC 61508-2);

- failure data collection is adequate (see 7.4.7.10 of IEC 61508-2);

- evidence is assessed taking into account the complexity of the subsystem, the contribution made by the subsystem to the risk reduction, the consequences associated with a failure of the subsystem, and the novelty of design (see 7.4.7.11 of IEC 61508-2); and

- the application of the proven in use subsystem is restricted to those functions and interfaces of the subsystem that meet the relevant requirements (see 7.4.7.12 of IEC 61508-2).

7.4.2.11 of IEC 61508-3 allows the use of standard or previously developed software without the availability of historical data but with the emphasis on analysis and testing. This concept should be distinguished from the proven in use concept described above.